Anaheim Integrated Circuit LSILS7166 User Manual

Here you can view all the pages of manual Anaheim Integrated Circuit LSILS7166 User Manual. The Anaheim manuals for Integrated Circuit are available online for free. You can easily download all the documents as PDF.

Page 1

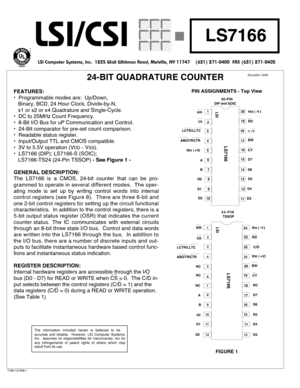

24-BIT QUADRATURE COUNTER

FEATURES:

• Programmable modes are: Up/Down,

Binary, BCD, 24 Hour Clock, Divide-by-N,

x1 or x2 or x4 Quadrature and Single-Cycle.

• DC to 25MHz Count Frequency.

• 8-Bit I/O Bus for uP Communication and Control.

• 24-Bit comparator for pre-set count comparison.

• Readable status register.

• Input/Output TTL and CMOS compatible.

• 3V to 5.5V operation (V

DD - VSS).

• LS7166 (DIP); LS7166-S (SOIC);

LS7166-TS24 (24-Pin TSSOP) - See Figure 1 -...

Page 2

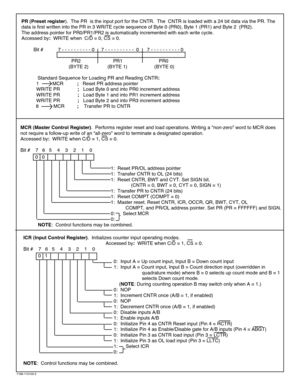

PR (Preset register). The PR is the input port for the CNTR. The CNTR is loaded with a 24 bit data via the PR. The

data is first written into the PR in 3 WRITE cycle sequence of Byte 0 (PR0), Byte 1 (PR1) and Byte 2 (PR2).

The address pointer for PR0/PR1/PR2 is automatically incremented with each write cycle.

Accessed by: WRITE when C/D = 0, CS = 0.

Bit # 7 - - - - - - - - - - 0 7 - - - - - - - - - - 0 7 - - - - - - - - - - 0...

Page 3

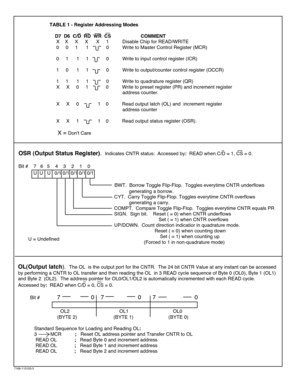

OSR (Output Status Register). Indicates CNTR status: Accessed by: READ when C/D = 1, CS = 0.

Bit # 7 6 5 4 3 2 1 0

U U U 0/1 0/1 0/1 0/1 0/1

BWT. Borrow Toggle Flip-Flop. Toggles everytime CNTR underflows

generating a borrow.

CYT. Carry Toggle...

Page 4

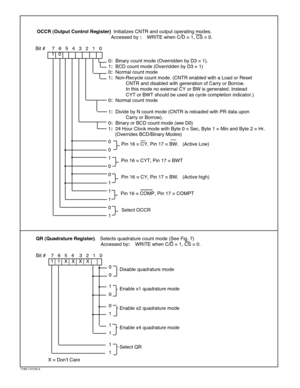

OCCR (Output Control Register) Initializes CNTR and output operating modes.

Accessed by : WRITE when C/D = 1, CS = 0.

Bit # 7 6 5 4 3 2 1 0

1 0

0: Binary count mode (Overridden by D3 = 1).

1: BCD count mode (Overridden by D3 = 1)

0: Normal count...

Page 5

DC Electrical Characteristics. (All voltages referenced to VSS.

T

A = 0˚ to 85˚C, VDD = 3V to 5.5V, fc = 0, unless otherwise specified)

Parameter Symbol Min. Value \

Max.Value Unit Remarks

Supply Voltage V

DD 3.0 5.5 V -

Supply Current I

DD- 350 µA Outputs open

Input Low Voltage V

IL0 0.8 V -

Input High Voltage V

IH 2.0 VDD V -

Output Low Voltage V

OL- 0.4...

Page 6

TRANSIENT CHARACTERISTICS (See Timing Diagrams in Fig. 2 thru Fig. 7,

VDD = 3V to 5.5V, TA = 0˚ to 85˚C, unless otherwise specified)

Parameter Symbol Min.Value Max.Value Unit

Clock A/B Low”TCL 18 No Limitns

Clock A/B HighTCH 22 No Limitns

Clock A/B Frequency fc 0 25MHz

(See NOTE 1)

Clock UP/DN ReversalTUDD100 -ns

Delay

LCTR Positive edge to TLC100 -ns

the next A/B positive or

negative edge...

Page 7

FIGURE 2 . LOAD COUNTER, UP CLOCK, DOWN CLOCK, COMPARE OUT, CARRY, BORR\ OW NOTE 1 : The counter in this example is assumed to be operating in the binary \ mode. NOTE 2 : No COMP output is generated here, although PR = CNTR. COMP output is \ disabled with a counter load command and enabled with the rising edge of the next clock, thus eliminating invali\ d COMP outputs whenever the CNTR is loaded from the PR. NOTE 3 : When UP Clock is active, the DN Clock should be held HIGH and vice \...

Page 8

Q1

(INTERNAL)

Q2-Q23 (INTERNAL)

DN CLK

LCTR

CNTR LD

(INTERNAL)

BW

Q0

(INTERNAL)

CNTR=3 =2 =1 =0 =3 =2 =1 =0 =3

FIGURE 5. DIVIDE BY N MODE

NOTE: EXAMPLE OF DIVIDE BY 4 IN DOWN COUNT MODE

CNTR DISABLED CNTR ENABLED CNTR DISABLED

CNTR LOAD

(LCTR or MCR BASED)

CY or BW

FIGURE 6 . CYCLE ONCE MODE

UP CLK ORDN CLK

7166-110103-8

C/D

WR

C/D RD

TCRSTCRH

DATA BUS TRD

VALID OUTPUT

TWR

TCWS

TCWH

DATA BUS

FIGURE 4. READ/WRITE CYCLES

VALID DATAT

DSTDH

TSWSTSWHCS

TRT

CS

TSRSTSRH

TRR

TWW

Page 9

7166-110503-9 TPH TPH A B UPCLK (x1)(Internal) DNCLK (x1)(Internal) UPCLK (x2) (Internal) DNCLK (x2) (Internal) UPCLK (x4)(Internal) DNCLK (x4) (Internal) FORWARDREVERSE UP/DN (OSR Bit 4) CY BW FIGURE 7. QUADRATURE MODE INTERNAL CLOCKS TCBW TCBW TCQV TCQV

Page 10

3 4 7 PR/OL ADDRESS INPUT BUFFER AND DECODE LOGIC (DATA-BUS) 8-15 I/O BUFFER D0 - D7 18 1 19 2 D0, D6,D7 D0 - D7 D0 - D7 D0 - D7 D0 -D7 5 20 (+5V) VDD (GND) VSS INTERNAL DATA BUS D0 -D4 QR OCCR ICR MCR PR0 B0 - B7 PR1 B8 - B15 PR2 DN CLOCK UP CLOCK D0 - D7 PR/OL ADDRESS B16 - B23 CNTR B0 - B23 N1=N2 N1 N2 STATUS LOGIC OL0OL1 OL2 Q0 -Q23 CONTROL LOGIC OSR FIGURE 8. LS7166 BLOCK DIAGRAM 6 (LOAD CTR/LOAD LATCH) LCTR/LLTC (AB GATE/LOAD LATCH) ABGT/RCTR (COUNT INPUT) B (COUNT INPUT) A...