Anaheim Integrated Circuit LSILS7366R Spec Sheet

Here you can view all the pages of manual Anaheim Integrated Circuit LSILS7366R Spec Sheet. The Anaheim manuals for Integrated Circuit are available online for free. You can easily download all the documents as PDF.

Page 1

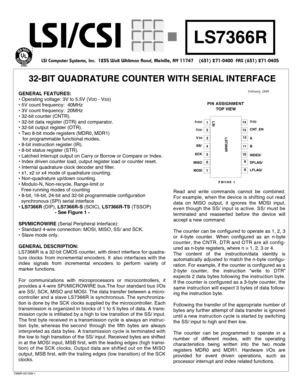

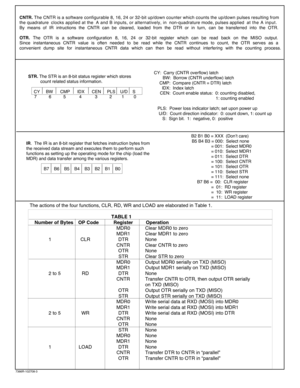

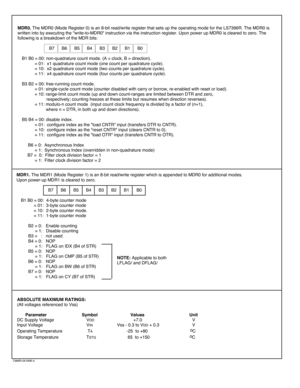

GENERAL FEATURES: • Operating voltage: 3V to 5.5V (V DD - VSS) • 5V count frequency: 40MHz • 3V count frequency: 20MHz • 32-bit counter (CNTR). • 32-bit data register (DTR) and comparator. • 32-bit output register (OTR). • Two 8-bit mode registers (MDR0, MDR1) for programmable functional modes. • 8-bit instruction register (IR). • 8-bit status register (STR). • Latched Interrupt output on Carry or Borrow or Compare or Index. • Index driven counter load, output register load or counter reset. •...

Page 2

7366R-081507-2I/O Pins: Following is a description of all the input/output pins. A (Pin 12) B (Pin 11) Inputs. A and B quadrature clock outputs from incremental encoders are directly applied to the A and B inputs of the LS7366R. These clocks are ideally 90 degrees out-of-phase signals. A and B inputs are validated by on-chip digital filters and then decoded for up/down direction and count clocks. In non-quadrature mode, A serves as the count input and B serves as the direction input (B = high enables up...

Page 3

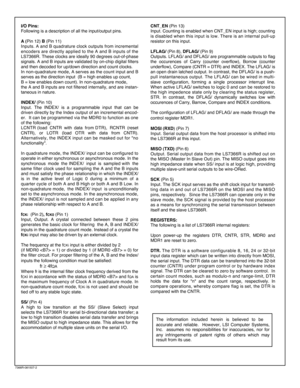

STR. The STR is an 8-bit status register which stores

count related status information.

CY BW CMP IDX CEN PLS U/D S

7 6 5 4 3 2 1 0

7366R-102708-3IR. The IR is an 8-bit register that fetches instruction bytes from

the received data stream and executes them to perform such

functions as setting up the operating mode for the chip (load the

MDR) and data transfer among the various registers.

B7...

Page 4

7366R-041906-4ABSOLUTE MAXIMUM RATINGS: (All voltages referenced to Vss) Parameter Symbol Values Unit DC Supply VoltageVDD +7.0V Input VoltageVIN Vss - 0.3 to VDD + 0.3 V Operating Temperature TA -25 to +80 o C Storage TemperatureTSTG 65 to +150 o C...

Page 5

DC Electrical Characteristics. (TA = -25˚C to +85°C) Parameter Symbol Min. TYP Max. Unit Remarks Supply Voltage VDD3.0-5.5V- Supply CurrentIDD300400450µAVDD = 3.0V IDD700800950µAVDD = 5.0V Input Voltages fCKi, Logic high VCH2.3--VVDD = 3.0V VCH3.7--VVDD = 5.0V fCKi, Logic Low VCL--0.7VVDD = 3.0V VCL--1.3VVDD = 5.0 All other inputs, Logic HighVAH2.1-VVDD = 3.0V VAH3.5-VVDD =...

Page 6

Parameter Symbol Min. Value \

Max.Value Unit Remarks

Non-Quadrature Mode

(See Fig. 6 & 9)

Clock A - High Pulse Width t

6 12 - ns -

Clock A - Low Pulse Width t

7 12 - ns -

Direction Input B Set-up Time t

8S 12 - ns -

Direction Input B Hold Time t

8H10 - ns -

CNT_EN Set-up Time t

9S 12 - ms -

CNT_EN Hold Time t

9H12 - ms...

Page 7

Note 1. The SPI port of the host MCU must be set up as follows:

1. SPI master mode.

2. SCK idle state = low

3. Clock edge for MOSI data shift = high to low

4. Clock edge for input data (MISO) sample by the Processor = low to high (or bit middle)

Note 2. To conform with the multibyte transmission protocol of LS7366R, the SS/ output port

of the MCU may require direct manipulation by the application program.

FIGURE 2. SPI TIMINGS7366R-041906-7 tCSH

tCL tCH...

Page 8

D7 D6 D5 D4 D3 D3 D2 D1 D0 D2D6 D5D7 D4 X X XRANDOM DATA X X X D1 D0 X SS/ SCK MOSI MISO BIT # 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 START OF NEW COMMAND RD MDR1 DATAWR MDR1tCSL BIT # 7 6 5 4 3 2 1 0 tCHtCL TRI-STATE D7 D6 D5 D4 D3 D3 D2 D1 D0 D2D6 D5D7 D4 XXX X X X D1 D0 SS/ SCK MOSI MISO BIT # 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 RD CNTR tCSI BIT # 7 6 5 4 3 2 1 0 BYTE 1 BYTE 0 CLR STR RANDOM DATA 7 6 5 4 3 2 1 0 TRI-STATE NOTE: Write to MDR1 followed by Read from MDR1 operation 7366R-120407-8...

Page 9

7366-081507-9

UP DOWN

A

B

X4_CLK

X2_CLK

X1_CLK

(see note)

(see note)

(see note)

tQ1

tQ2

Note: x1, x2, and x4 CLKs are internal up/down clocks derived from filtered a\

nd decoded quadrature clocks.

FIGURE 7. A/B QUADRATURE CLOCKS vs INTERNAL C\

OUNT CLOCKS

Note: CNTR values are indicated in 3-byte mode

FIGURE 8. QUADRATURE CLOCKS v\

s FLAG OUTPUTS

FIGURE 6. COUNT...

Page 10

7366R-050106-10

NOTE: CNTR values are indicated in 2-byte mode

FIGURE 9. SINGLE-CYCLE, NON-QUADRATURE

NOTE: CNTR values are indicated in 1-byte mode

FIGURE 10. MODULO-N, NON-QUADRATURE

NOTE: CNTR values are indicated in 1-byte mode

FIGURE 11. RANGE-LIMIT, NON-QUADRATURE

INDX/ DFLG/CNTR

A B

FFFFFFCFFFFFFDFFFFFFEFFFFFFF 0

2 1 0FFFFFFF

CY

t9t10

t11CNTR DISABLED CNTR DISABLED

(Shown with DTR = 2)

CNTR ENABLED

(LOAD CNTR)

UP DOWN

DFLAG/ CNTR

A...